浅谈芯片设计软件EDA 数字世界的“画笔”与“基石”

在当今这个由智能手机、智能汽车、高性能计算和万物互联定义的时代,芯片无疑是驱动这一切的“数字心脏”。而在这颗心脏被物理制造出来之前,其复杂到极致的蓝图——从架构规划到电路布局,从逻辑验证到物理实现——几乎全部依赖于一类特殊的软件工具来完成。这就是电子设计自动化软件,简称EDA。它不仅是芯片设计的必备工具,更是整个半导体产业的战略制高点和技术基石。

一、EDA:芯片设计的“全栈工具箱”

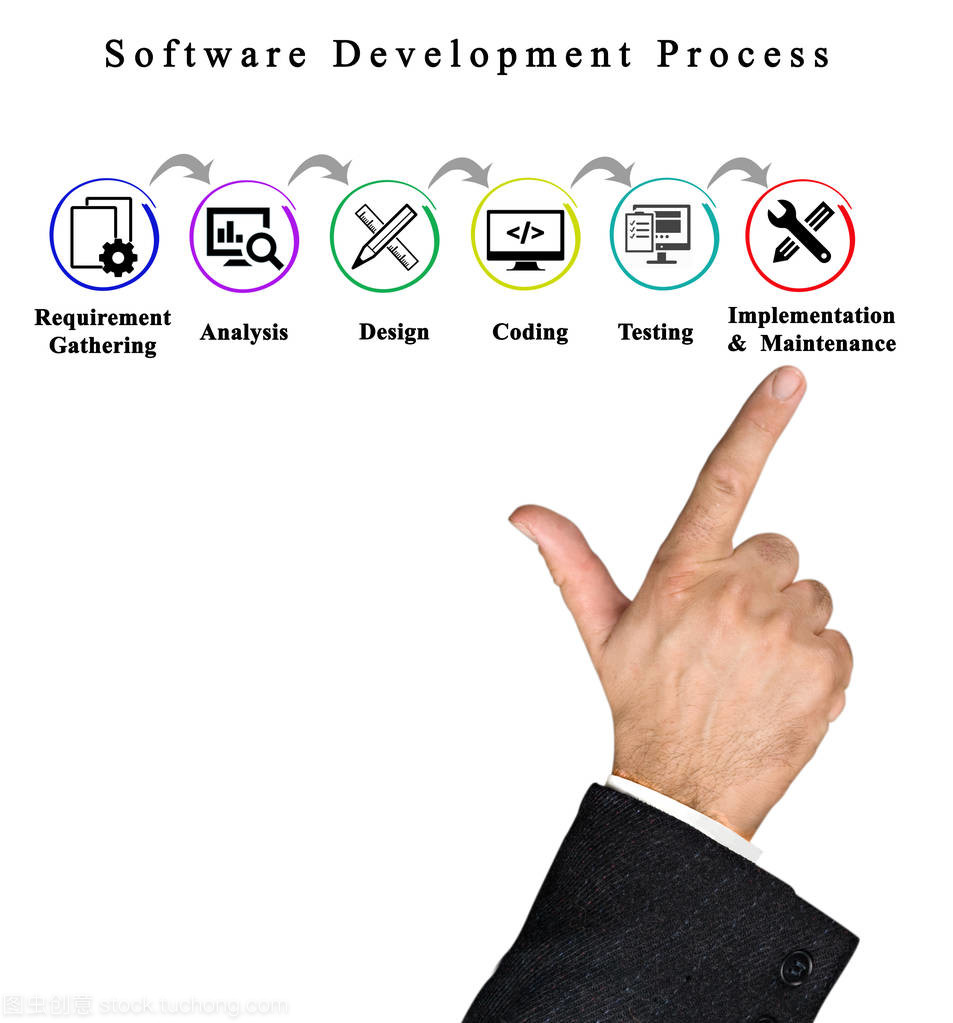

EDA并非单一软件,而是一个庞大、复杂且高度集成的软件工具链生态系统。其核心使命是协助工程师将抽象的电路构想,转化为可供晶圆厂制造的具体物理版图。这个过程通常涉及多个层级:

- 前端设计:这是芯片设计的“灵魂”阶段。工程师使用硬件描述语言(如Verilog, VHDL)在EDA工具中描述芯片的功能和逻辑行为。此阶段的核心工具包括:

- 设计输入与仿真:用于编写和模拟验证代码逻辑的正确性。

- 逻辑综合:将高级的HDL代码“翻译”成由基本逻辑门(如与门、或门)构成的网表,是连接抽象设计与后端物理实现的关键桥梁。

- 形式验证:通过数学方法严格证明设计在不同阶段的一致性,确保转换过程无错误。

- 后端设计:这是芯片设计的“躯体”塑造阶段。任务是将逻辑网表转化为真实的、符合制造规则的物理版图。此阶段挑战巨大,涉及:

- 布局布线:决定数十亿乃至数百亿个晶体管在硅片上的具体位置,并用“金属线”将它们精确连接起来。这是EDA技术皇冠上的明珠,需要处理速度、功耗、面积和信号完整性等多重目标的极端优化。

- 物理验证:检查版图是否符合晶圆厂的制造工艺规则,并分析时序、功耗、电迁移、信号串扰等物理效应。

- 可制造性设计:预先考虑制造过程中的偏差,通过添加辅助图形等方式,提高芯片的最终良率。

随着工艺进入纳米尺度(如3nm、2nm),芯片设计已步入“系统级”和“三维”时代,EDA工具还涵盖了系统架构探索、芯片-封装协同设计、光电融合设计等前沿领域。

二、EDA软件开发:交叉学科的巅峰挑战

开发一款业界领先的EDA工具,是一项集算法、软件工程、半导体物理和集成电路设计于一体的超级工程。其核心挑战在于:

- 算法复杂度:布局布线、时序分析、功耗分析等问题本质上是NP-hard的优化问题。开发团队需要创造性地设计启发式算法、机器学习模型,并利用高性能计算(HPC)进行并行加速,以在可接受的时间内处理海量数据。

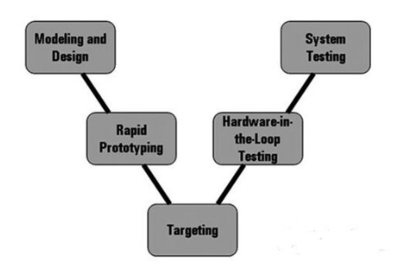

- 精度与效率的平衡:芯片设计不容有失,但仿真和验证又必须快速。EDA软件需要在快速但粗略的估算与精确但耗时的计算之间找到最佳平衡点,通常采用多层次、多精度的验证流程。

- 与工艺的深度绑定:EDA工具必须紧跟半导体制造工艺的演进。每一代新工艺(如FinFET、GAA晶体管)的物理特性、设计规则都完全不同,要求EDA软件内核进行根本性的更新和适配。这使得EDA公司与晶圆厂(如台积电、三星)的合作密不可分。

- 数据与生态:现代EDA平台正演变为“数据驱动”和“云原生”的设计环境。利用AI/ML技术预测设计效果、自动优化参数,以及构建基于云端的协同设计平台,是当前研发的重点方向。

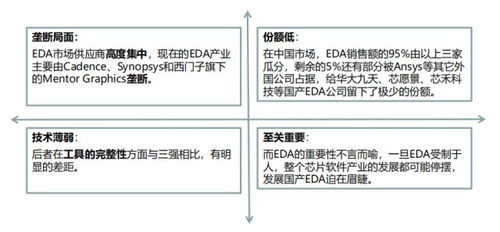

三、产业格局与未来展望

全球EDA市场呈现高度集中的格局,主要由新思科技、铿腾电子和西门子EDA三家巨头主导,它们提供了覆盖全流程的完整解决方案。这一领域技术壁垒极高,需要长期的研发投入、深厚的专利积累和广泛的客户生态。

EDA的发展趋势清晰可见:

- AI赋能设计:AI将更深地融入从架构探索到布局布线的各个环节,实现“AI设计芯片,芯片驱动AI”的闭环。

- 系统级与异构集成:面向Chiplet(芯粒)和3D堆叠等先进封装技术的EDA工具将成为关键,管理多芯片、多工艺、多物理域的协同设计与验证。

- 开放与标准化:为了降低设计门槛和促进创新,开源EDA工具(如OpenROAD)和标准接口(如UCIe)正获得越来越多的关注。

- 安全与可靠性:随着芯片应用于汽车、航天等安全关键领域,功能安全、信息安全的设计与验证工具变得至关重要。

总而言之,EDA是芯片创新不可或缺的“引擎”和“放大器”。它让人类驾驭晶体管海洋的梦想成为可能,将天马行空的电路创意固化为精密的硅基实体。在半导体产业自主可控的宏大叙事下,发展自主可控的高端EDA软件,其战略意义不亚于制造芯片本身。它不仅是软件,更是凝结了人类顶尖智慧、推动数字文明向前发展的关键基石。

如若转载,请注明出处:http://www.shangshangying.com/product/56.html

更新时间:2026-04-14 22:30:10